### **Overview**

The IB-ASRC-H is part of the IPbloq family of multichannel Asynchronous Audio Sample Rate Converters (ASRCs). This IP core can be used in systems on chip for consumer or professional audio applications. It has been designed for systems requiring very high quality in terms of low harmonic distortion and noise, tolerance and rejection of input jitter.

### **Features**

- · Fully digital IP core

- Pre-synthesis configurable up to 8 audio channels

- Automatically adjusts to input and output sample rate changes

- Input and output sample rate range: 8 kHz to 192 kHz

- Sampling rate conversion ratios from 1:7 to 7:1

- Supports multi-channel TDM serial/parallel audio, I2S, AES3/SPDIF

- Tolerates and rejects input jitter

- Latency:  $128/FS_{IN} + 2/FS_{OUT}$

- -130 dB THD+N and Dynamic Range

- Reports sample rate conversion ratio in real time

- Fast synchronization time: 128 input sample periods

- $\bullet$  Pre-synthesis Clk OUT configuration from  $64\times FS_{OUT}$  to  $1024\times FS_{OUT}$

#### **Benefits**

- Eliminates need for a discrete ASRC chip in the BOM

- Supported in both FPGA and ASIC

- Scalable architecture allows features to be added upon request

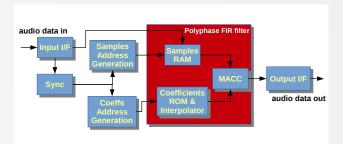

# **Block Diagram**

Table 1: Results for Xilinx FPGAs

| FPGA      | SLICES | BRAM<br>9 kb | BRAM<br>18 kb | BRAM<br>36 kb | DSPs |

|-----------|--------|--------------|---------------|---------------|------|

| Spartan-6 | 700    | 0            | 16            | N/A           | 6    |

| Kintex-7  | 700    | N/A          | 0             | 9             | 4    |

| Virtex-7  | 650    | N/A          | 0             | 9             | 4    |

Table 2: Results for ASIC implementation

| TSMC<br>NODE | CELLS | AREA (mm <sup>2</sup> ) | Max<br>CLK₋IN<br>(MHz) | Max<br>CLK₋OUT<br>(MHz) |

|--------------|-------|-------------------------|------------------------|-------------------------|

| 65nm         | 9200  | 0.04                    | 475                    | 200                     |

| 45nm         | 9850  | 0.02                    | 600                    | 275                     |

### **Deliverables**

- Datasheet and user documentation for system integration

- RTL code in Verilog or FPGA netlist

- RTL testbench

- Synthesis and implementation constraints

# Contact information

Web: www.ipbloq.com info@ipbloq.com

Address: Rua Dona Estefânia, 98-2E

1000-158 Lisboa

Portugal

Disclaimer: IPBloq reserves the right to modify the current technical specifications without notice.